# Universität Stuttgart

Institut für Robuste Leistungshalbleitersysteme

M.Sc. Laura Manoliu Pfaffenwaldring 32, 70569 Stuttgart Interimsgebäude 1 +49 711 685-61685 Iaura.manoliu@ilh.uni-stuttgart.de

27.07.2020

the on-board AWG implemented on FPGA for a satellite mission

**EVM optimization for**

www.eive.space

Bachelor/Research/Master Thesis – Bachelor-/Forschung/Master-Arbeit

HF

FIVE

### Project:

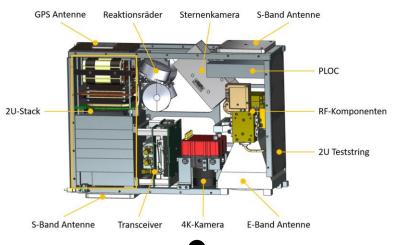

In the framework of the EIVE Project the Institute of Robust Power Semiconductor Systems (ILH) is developing a 6-Unit CubeSat, flying in the Low Earth Orbit (LEO). An arbitrary waveform generator (AWG) has to be efficiently implemented in Programming Logic (FPGA) and Programming Software (CPU).

#### **Scientific Mission:**

- (1) PRBS transmission with various modulation schemes (QPSK, n-QAM, ...) and different data rates for in-depth data-link analysis;

- (2) E-Band Link Budget calculation, considering all the atmospheric effects;

- (3) Download high resolution images stored onboard for Earth observation applications.

#### Your Tasks:

- Investigate possible coding/filter algorithms for the raw PRBS data to improve the system (FPGA+DAC) Error Vector Magnitude (EVM);

- 2. Implement on the FPGA and on the CPU the selected algorithms and draw the conclusion about the energy efficiency and feasibility;

- 3. Measure the resulting EVM in different scenarios;

- 4. (Optional) Implement the decoding algorithms in the receiver.

#### Your Benefits:

- Consolidate your knowledge in various (satellite) communication systems;

- 2. Get ready for a (space) industry career;

- 3. Learn about different coding techniques;

- 4. Learn about FPGAs and DACs and acquire hands-on experience;

- Learn about digital and analogue communication systems to provide high performance radio communication solutions;

- 6. Develop team working skills.

German description also available at request.

## Your Qualifications:

- Digital communication systems/algorithms knowledge;

- Hands-on experience in developing C/Matlab/Python codes;

- Knowledge with software development: VHDL and/or Verilog, Xilinx Vivado is advantageous;

- Passionate for producing high-quality, space-ready and well-tested code;

- Knowledge of analogue communication systems is a plus;

- Knowledge of communication protocols is an asset;

- Availability for team working is required.